Lisa Su's dirty little "secret sandbagging" during her CES presentation.

Lisa Su's dirty little "secret sandbagging" during her CES presentation. Lisa held up a TSMC 7nm lithography Vega

10 unit APU (complete with enlarged AI block and wider data paths) matched up with a TSMC 7nm lithography

8 core CPU block and

then simply didn't say one more word about it.

All she spoke to was a mild one upping of the rather disappointing 11-12nm Intel "10nm" performance as promised by Intel in the "end of 2019 in the far distant future".

Lisa Su was simply doing some classical sandbagging, in other words .......One potential reason for this sandbagging reticence is large existing stocks of older AMD units that are not moving as quickly as were originally hoped ---- upgrading your own inventory for the 3rd time in two years might tend to hurt your own financials if that is done in a precipitous fashion.

AMD needs to sell off their channel full of old stuff before replacing it whole hog with much more desirable items. Once the much better stuff is out all demand for the older style stuff

ends abruptly ......

Intel's ongoing production shortfalls will continue to move AMD's older units (especially when the older units are properly priced) but

it needs some time to work it all through as the whole PC market is somewhat soft at the moment. TSMC will also get even better at 7nm full production during the meantime, increasing AMD's production yields and lowering the net price per wafer accordingly.

AMD can also continue to work on their 5nm stuff, getting it ready as well. 7nm is likely to be a short lived node anyway since the same equipment can run 5nm parts ...... this is both known and proven real by both TSMC and Samsung who already own the direct burn EUV lines that can do this trick.

Note please that Samsung and IBM just made a contract to run IBM's 5nm stuff at Samsung, this 5nm agreement is about the same cooperative agreement as they inked 2 years ago about 7nm lithography.

===================================================

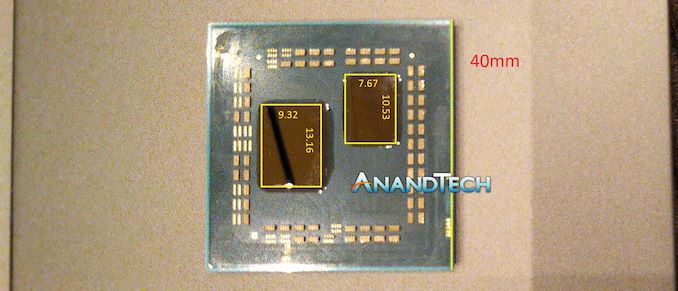

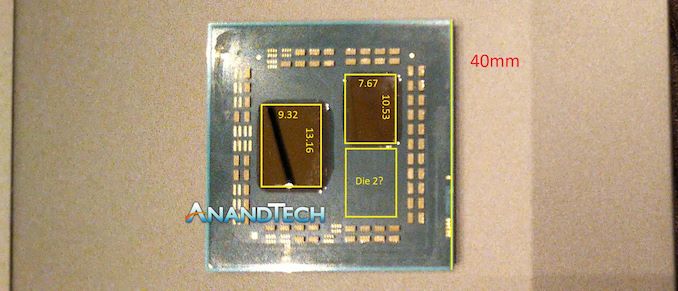

https://www.anandtech.com/show/13829/amd-ryzen-3rd-generation-zen-2-pcie-4-ei...Further "confusions" stemming from Lisa Su's presentation at CESWhen Lisa shows the silicon set and talks about APUs coming out now and again in mid year she is showing and talking APUs (combined graphics and processing units). These are the new AMD

laptop chipsets that are rolling out right now as we speak ......

When she is talking Mattisse, that is a desktop set up has no graphics unit in the big chip per se ....... it is a desktop processor that always has 1 each 8 core 7nm CPU chiplet built at TSMC. Mattisse can then have a larger lithography 12-14nm I/O chiplet that is built at Global due to production constraints (or lower pricing, got to remember that). The Mattisse CPU core chiplets are always the same 7nm TSMC as in APU, but the I/O chiplet on Mattisse is much much simpler and can be done at older lesser lithography levels very easily.

Remember, Mattisse and APU both swing two core filled die sets at this time, one is an I/O (and always has the on die rapid access buffer memory in it). In the APU case the big chiplet includes Vega graphics cores (up to 10 of them). In the Mattisse case the big chiplet does not include any graphics, just I/O and rapid access buffer memory.

Confusing?

Oh my yes -- now take these scenarios and add it to your confusion. A failed sorted APU unit may be sorted and sold as a Mattisse graphic-less variant with the failed graphics seared off.

On the 7nm Cpu chiplet side, sorted small CPU chiplets may have 1-4 non-functional compute cores seared off as well.

In full complexity of sorting, an I/O chip may start out intended as a 7nm TSMC based APU with up to 10 Vega graphics cores and an AI block inside the larger I/O chiplet on an AM4 socket silicon with 8 cores of 7nm TSMC CPU cores inside the smaller chiplet, and these CPU cores can be seared off as well to potentially lose all the the graphics and also lose one or more CPU cores in sorting.

So you got variants possible that have had graphics but lost them and had up to 8 compute CPU cores but lost some of those. Or the variant can be built on purpose to never have had them in the first place if the demand is there and there aren't enough sorted units to meet the need.

WHAT IS LEFT HAS NOT BEEN SHOWN AND EXISTS ONLY OUT THERE IN THE FUTURE

WHAT IS LEFT HAS NOT BEEN SHOWN AND EXISTS ONLY OUT THERE IN THE FUTURE (for sometimes for when Lisa Su decides it is needed).

This is the 12-16 core cpu (dual CPU chiplet) variant that is NOT NEEDED right now to keep up with Intel's best of the best i7-9970 8 core chipset --- Intel tops out at 8 cores in consumer at the moment and AMD will be content to outdo 8 core Intel using 8 better 7nm cores from TSMC.

This 12-16 core variant will not exist in Consumer until Intel actually goes there inside normal consumer computing.NOTE: This variant technically already exists in Server space, where Intel already has 16 cores per die (with 2 separate sockets per motherboard) and AMD has up to 32 cores per die right now using the chiplet technology (but it is on the larger single Epic server die set and socket scenario).

Intel is the one who likes to plug their old server die sets and sockets into Consumer space, they have done it several times already.

So far AMD likes to re-use the AM4 socket die set over and over, using smaller and smaller TSMC lithography in roughly the same sized chiplets to make it work again and again and again -- filling the space up with more and more cores as the lithography shrinks happen.

5nm chiplets are certainly out there in the future on the AM4 socket die, this is a no brainer coming from AMD. Core counts will likely start at 8 and go to 16 and mebbe go to 32 potentially when 3nm comes around, all staying in the AM4 socket size.The AMD Epic server socket and die also will roll out with 5nm and 3nm chiplets when those waves begin, but your guess is as good as mine as to what the core counts will eventually be. Many many, obviously --- 64 cores being the most likely next expansion.

Intel re-dies and re-busses their old motherboards at a bi-yearly pace, while AMD shows repeatedly they can use the same board and the same socket with just a BIOS refresh.